# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

*H01L* 27/15 (2006.01) *G09F* 9/33 (2006.01) *H01L* 21/768 (2006.01) *H01L* 33/00 (2010.01)

(52) CPC특허분류 *H01L 27/156* (2013.01) *G09F 9/33* (2013.01)

(21) 출원번호 **10-2020-0019246**

(22) 출원일자 **2020년02월17일**

심사청구일자 없음

(11) 공개번호 10-2020-0024177

(43) 공개일자 2020년03월06일

(71) 출원인

엘지전자 주식회사

서울특별시 영등포구 여의대로 128 (여의도동)

(72) 발명자

장재원

서울특별시 서초구 양재대로11길 19

김수현

서울특별시 서초구 양재대로11길 19

(74) 대리인 **박장원**

전체 청구항 수 : 총 10 항

#### (54) 발명의 명칭 디스플레이 장치의 제조방법 및 디스플레이 장치 제조를 위한 기판

#### (57) 요 약

본 발명은 디스플레이 장치의 제조방법에 관한 것으로 특히, 수㎞ 내지 수십㎞ 크기의 반도체 발광소자를 이용한 디스플레이 장치의 제조 방법 및 디스플레이 장치 제조에 사용되는 조립 기판에 관한 것이다. 상술한 목적을 달성하기 위하여, 본 발명은 전기장 및 자기장을 이용하여 반도체 발광소자들을 조립 기판의 기 설정된 위치로 안착 시키는, 디스플레이 장치의 제조 방법에 사용되는 조립 기판을 제공한다. 구체적으로, 상기 조립 기판은 베이스부, 상기 베이스부 상에 형성되는 보조 전극들, 상기 보조 전극들을 덮도록, 상기 베이스부 상에 형성되는 절연층, 상기 절연층 상에 배치되는 복수의 조립 전극들, 반도체 발광소자들을 기 설정된 위치로 가이드하는 복수의 홈을 구비하고, 상기 베이스부 상에 형성되는 격벽을 포함하고, 상기 보조 전극의 일부는 상기 조립 전극과 오버랩되도록 배치되는 것을 특징으로 한다.

#### 대 표 도 - 도13

## (52) CPC특허분류

H01L 21/76895 (2013.01) H01L 33/005 (2013.01) H01L 2224/0344 (2013.01)

### 명세서

#### 청구범위

#### 청구항 1

전기장 및 자기장을 이용하여 반도체 발광소자들을 조립 기판의 기 설정된 위치로 안착 시키는, 디스플레이 장치의 제조 방법에 사용되는 조립 기판에 있어서,

상기 조립 기판은,

#### 베이스부;

상기 베이스부 상에 형성되는 보조 전극들;

상기 보조 전극들을 덮도록, 상기 베이스부 상에 형성되는 절연층;

상기 절연층 상에 배치되는 복수의 조립 전극들;

반도체 발광소자들을 기 설정된 위치로 가이드하는 복수의 홈을 구비하고, 상기 베이스부 상에 형성되는 격벽을 포함하고,

상기 보조 전극의 일부는 상기 조립 전극과 오버랩되도록 배치되는 것을 특징으로 하는 조립 기판.

#### 청구항 2

제1항에 있어서,

상기 조립 전극들 각각은 상기 조립 전극이 연장되는 방향과 교차하는 방향으로 돌출되는 제1돌출부를 구비하고,

상기 보조 전극은 상기 제1돌출부와 오버랩되도록 배치되는 것을 특징으로 하는 조립 기판.

### 청구항 3

제2항에 있어서,

상기 조립 전극들 각각은 상기 홈과 오버랩되도록 형성되며, 상기 조립 전극이 연장되는 방향과 교차하는 방향으로 돌출되는 제2돌출부를 구비하는 것을 특징으로 하는 조립 기판.

#### 청구항 4

제3항에 있어서.

상기 보조 전극들은,

상기 홈과 오버랩되지 않도록 형성되는 것을 특징으로 하는 조립 기판.

### 청구항 5

제1항에 있어서,

상기 격벽과 상기 조립 전극들 사이에 배치되는 유전체층을 더 포함하는 것을 특징으로 하는 조립 기판.

#### 청구항 6

제1항에 있어서,

상기 조립 전극과 상기 보조 전극이 오버랩되는 영역에서,

상기 조립 전극과 상기 보조 전극 사이의 정전용량은 1fF 내지 5000μF인 것을 특징으로 하는 조립 기판.

#### 청구항 7

복수의 조립 전극들, 상기 조립 전극들과 오버랩되도록 배치되는 복수의 보조 전극들 및 복수의 홈을 포함하는 격벽을 구비하는 조립 기판을 조립위치로 이송하고, 반도체 발광소자들을 유체 챔버에 투입하는 단계;

상기 유체 챔버 내에서 상기 반도체 발광소자들이 일방향을 따라 이동하도록, 상기 반도체 발광소자들에 자기력을 가하는 단계;

상기 반도체 발광소자들이 일 방향을 따라 이동하는 중 상기 조립 전극들 사이에 전기장을 형성되는 전기장에 의하여 상기 반도체 발광소자들이 상기 홈 내부로 유도되도록, 상기 조립 전극들 사이에서 전기장을 발생시키는 단계를 포함하고,

상기 조립 전극들 사이에서 전기장을 발생시키는 단계는,

상기 조립 전극들과 상기 보조 전극들 사이에 전하를 충전하는 단계; 및

상기 조립 전극들과 상기 보조 전극들 사이에 충전된 전하를 이용하여 상기 조립 전극들 각각에 인가되는 전압의 크기를 증폭시키는 단계를 포함하는 것을 특징으로 하는 디스플레이 장치의 제조방법.

#### 청구항 8

제7항에 있어서.

상기 조립 전극들과 상기 보조 전극들 사이에 전하를 충전하는 단계는,

상기 조립 전극들과 상기 보조 전극들 각각에 전압을 인가함으로써 수행되는 것을 특징으로 하는 디스플레이 장치의 제조방법.

#### 청구항 9

제8항에 있어서,

상기 조립 전극들 각각에 인가되는 전압의 크기를 증폭시키는 단계는,

상기 조립 전극들 각각에 인가되는 전압을 차단함으로써 수행되는 것을 특징으로 하는 디스플레이 장치의 제조 방법.

#### 청구항 10

제9항에 있어서,

상기 조립 전극들 각각에 인가되는 전압의 크기를 증폭시키는 단계에서 상기 보조 전극들에 인가되는 전압의 절대값은 상기 조립 전극들과 상기 보조 전극들 사이에 전하를 충전하는 단계에서 상기 보조 전극들에 인가되는 전압의 절대값보다 큰 것을 특징으로 하는 디스플레이 장치의 제조방법.

#### 발명의 설명

#### 기술분야

[0001] 본 발명은 디스플레이 장치의 제조방법에 관한 것으로 특히, 수/m 내지 수십/m 크기의 반도체 발광소자를 이용한 디스플레이 장치의 제조 방법 및 디스플레이 장치 제조에 사용되는 조립 기판에 관한 것이다.

#### 배경기술

- [0002] 최근에는 디스플레이 기술분야에서 대면적 디스플레이를 구현하기 위하여, 액정 디스플레이(LCD), 유기 발광 소자(OLED) 디스플레이, 그리고 마이크로 LED 디스플레이 등이 경쟁하고 있다.

- [0003] 한편, 디스플레이에 100 마이크론 이하의 직경 또는 단면적을 가지는 반도체 발광소자(마이크로 LED (uLED))를 사용하면 디스플레이가 편광판 등을 사용하여 빛을 흡수하지 않기 때문에 매우 높은 효율을 제공할 수 있다. 그러나 대형 디스플레이에는 수백만 개의 반도체 발광소자들을 필요로 하기 때문에 다른 기술에 비해 소자들을 전사하는 것이 어려운 단점이 있다.

- [0004] 전사공정으로 현재 개발되고 있는 기술은 픽앤플레이스(pick & place), 레이저 리프트 오프법(Laser Lift-off, LLO) 또는 자가조립 등이 있다. 이 중에서, 자가조립 방식은 유체내에서 반도체 발광소자가 스스로 위치를 찾아

가는 방식으로서, 대화면의 디스플레이 장치의 구현에 가장 유리한 방식이다.

[0005] 최근에는 미국등록특허 제9,825,202에서 자가조립에 적합한 마이크로 LED 구조를 제시한 바 있으나, 아직 마이크로 LED의 자가조립을 통하여 디스플레이를 제조하는 기술에 대한 연구가 미비한 실정이다. 이에, 본 발명에서는 마이크로 LED가 자가조립될 수 있는 새로운 형태의 제조방법을 제시한다.

#### 발명의 내용

#### 해결하려는 과제

- [0006] 본 발명의 일 목적은 마이크로 크기의 반도체 발광소자를 사용한 대화면 디스플레이에서, 높은 신뢰성을 가지는 새로운 제조공정을 제공하는 것이다.

- [0007] 본 발명의 또 다른 일 목적은 반도체 발광소자를 조립 기판으로 자가조립할 때에, 전사 정밀도를 향상시킬 수 있는 제조공정을 제공하기 위한 것이다.

- [0008] 본 발명의 또 다른 일 목적은 수 내지 수십 마이크로미터 크기의 반도체 발광소자를 수십 마이크로미터 이내의 간격으로 자가조립할 때, 전사 정밀도를 향상시킬 수 있는 조립 기판의 구조를 제공하기 위한 것이다.

- [0009] 본 발명의 또 다른 일 목적은 자가조립 시 조립 전극들 사이에 형성되는 전기장의 세기를 증폭시킬 수 있는 조립 기판의 구조를 제공하기 위한 것이다.

#### 과제의 해결 수단

- [0010] 상술한 목적을 달성하기 위하여, 본 발명은 전기장 및 자기장을 이용하여 반도체 발광소자들을 조립 기판의 기설정된 위치로 안착 시키는, 디스플레이 장치의 제조 방법에 사용되는 조립 기판을 제공한다. 구체적으로, 상기조립 기판은 베이스부, 상기 베이스부 상에 형성되는 보조 전극들, 상기 보조 전극들을 덮도록, 상기 베이스부 상에 형성되는 절연층, 상기 절연층 상에 배치되는 복수의 조립 전극들, 반도체 발광소자들을 기 설정된 위치로 가이드하는 복수의 홈을 구비하고, 상기 베이스부 상에 형성되는 격벽을 포함하고, 상기 보조 전극의 일부는 상기 조립 전극과 오버랩되도록 배치되는 것을 특징으로 한다.

- [0011] 일 실시 예에 있어서, 상기 조립 전극들 각각은 상기 조립 전극이 연장되는 방향과 교차하는 방향으로 돌출되는 제1돌출부를 구비하고, 상기 보조 전극은 상기 제1돌출부와 오버랩되도록 배치될 수 있다.

- [0012] 일 실시 예에 있어서, 상기 조립 전극들 각각은 상기 홈과 오버랩되도록 형성되며, 상기 조립 전극이 연장되는 방향과 교차하는 방향으로 돌출되는 제2돌출부를 구비할 수 있다.

- [0013] 일 실시 예에 있어서, 상기 보조 전극들은 상기 홈과 오버랩되지 않도록 형성될 수 있다.

- [0014] 일 실시 예에 있어서, 본 발명은 상기 격벽과 상기 조립 전극들 사이에 배치되는 유전체충을 더 포함할 수 있다.

- [0015] 일 실시 예에 있어서, 상기 조립 전극과 상기 보조 전극이 오버랩되는 영역에서, 상기 조립 전극과 상기 보조 전극 사이의 정전용량은 1fF 내지 5000  $\mu$ F일 수 있다.

- [0016] 또한, 본 발명은 복수의 조립 전극들, 상기 조립 전극들과 오버랩되도록 배치되는 복수의 보조 전극들 및 복수의 홈을 포함하는 격벽을 구비하는 조립 기판을 조립위치로 이송하고, 반도체 발광소자들을 유체 챔버에 투입하는 단계, 상기 유체 챔버 내에서 상기 반도체 발광소자들이 일방향을 따라 이동하도록, 상기 반도체 발광소자들에 자기력을 가하는 단계, 상기 반도체 발광소자들이 일 방향을 따라 이동하는 중 상기 조립 전극들 사이에 전 기장을 형성되는 전기장에 의하여 상기 반도체 발광소자들이 상기 홈 내부로 유도되도록, 상기 조립 전극들 사이에서 전기장을 발생시키는 단계를 포함하고, 상기 조립 전극들 사이에서 전기장을 발생시키는 단계는 상기 조립 전극들과 상기 보조 전극들 사이에 전하를 충전하는 단계 및 상기 조립 전극들과 상기 보조 전극들 사이에 충전된 전하를 이용하여 상기 조립 전극들 각각에 인가되는 전압의 크기를 증폭시키는 단계를 포함하는 것을 특징으로 하는 디스플레이 장치의 제조방법을 제공한다.

- [0017] 일 실시 예에 있어서, 상기 조립 전극들과 상기 보조 전극들 사이에 전하를 충전하는 단계는, 상기 조립 전극들 과 상기 보조 전극들 각각에 전압을 인가함으로써 수행될 수 있다.

- [0018] 일 실시 예에 있어서, 상기 조립 전극들 각각에 인가되는 전압의 크기를 증폭시키는 단계는, 상기 조립 전극들

각각에 인가되는 전압을 차단함으로써 수행될 수 있다.

[0019] 일 실시 예에 있어서, 상기 조립 전극들 각각에 인가되는 전압의 크기를 증폭시키는 단계에서 상기 보조 전극들 에 인가되는 전압의 절대값은 상기 조립 전극들과 상기 보조 전극들 사이에 전하를 충전하는 단계에서 상기 보조 전극들에 인가되는 전압의 절대값보다 클 수 있다.

#### 발명의 효과

- [0020] 상기와 같은 구성의 본 발명에 의하면, 개별화소를 마이크로 발광 다이오드로 형성하는 디스플레이 장치에서, 다량의 반도체 발광소자를 한 번에 조립할 수 있다.

- [0021] 이와 같이, 본 발명에 따르면 작은 크기의 웨이퍼 상에서 반도체 발광소자를 다량으로 화소화시킨 후 대면적 기 판으로 전사시키는 것이 가능하게 된다. 이를 통하여, 저렴한 비용으로 대면적의 디스플레이 장치를 제작하는 것이 가능하게 된다.

- [0022] 또한, 본 발명의 제조방법에 따르면, 용액 중에 자기장과 전기장을 이용하여 반도체 발광소자를 정위치에 동시다발적으로 전사함으로, 부품의 크기나 개수, 전사 면적에 상관없이 저비용, 고효율, 고속 전사 구현이 가능하다.

- [0023] 나아가, 전기장에 의한 조립이기 때문에 별도의 추가적인 장치나 공정없이 선별적 전기적 인가를 통하여 선택적 조립이 가능하게 된다. 또한, 조립 기판을 챔버의 상측에 배치함으로 기판의 로딩 및 언로딩이 용이하며, loading, unloading을 용이하게 하고, 반도체 발광소자의 비특이적 결합이 방지될 수 있다.

- [0024] 본 발명에 따르면, 조립 전극과 보조 전극 사이에 충전된 전하를 이용하여 조립 전극에 인가되는 전압의 크기를 전원 공급부에서 인가할 수 있는 최대 전압이상으로 증가시킬 수 있게 된다. 이를 통해, 본 발명은 별도의 증폭기를 도입하지 않고도, 조립 전극들 사이에 형성되는 전기장의 세기를 증폭시킬 수 있게 된다.

#### 도면의 간단한 설명

- [0025] 도 1은 본 발명의 반도체 발광 소자를 이용한 디스플레이 장치의 일 실시예를 나타내는 개념도이다.

- 도 2는 도 1의 디스플레이 장치의 A 부분의 부분 확대도이다.

- 도 3은 도 2의 반도체 발광소자의 확대도이다.

- 도 4는 도 2의 반도체 발광소자의 다른 실시예를 나타내는 확대도이다.

- 도 5a 내지 도 5e는 전술한 반도체 발광 소자를 제작하는 새로운 공정을 설명하기 위한 개념도들이다.

- 도 6은 본 발명에 따른 반도체 발광소자의 자가조립 장치의 일 예를 나타내는 개념도이다.

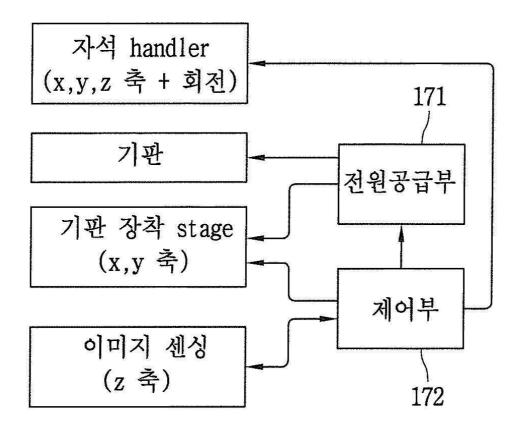

- 도 7은 도 6의 자가조립 장치의 블록 다이어그램이다.

- 도 8a 내지 도 8e는 도 6의 자가조립 장치를 이용하여 반도체 발광소자를 자가조립하는 공정을 나타내는 개념도 이다.

- 도 9는 도 8a 내지 도 8e의 반도체 발광소자를 설명하기 위한 개념도이다.

- 도 10은 도 8a 내지 8e에서 설명한 조립 전극을 나타낸 평면도이다.

- 도 11은 도 8a 내지 8e에서 설명한 조립 기판의 회로도이다.

- 도 12는 도 11에서 설명한 회로에 인가되는 조립 신호를 나타내는 개념도이다.

- 도 13은 본 발명에 따른 조립 기판을 나타내는 평면도이다.

- 도 14a는 도 13에서 설명한 조립 기판을 라인 A-A'를 따라 자른 단면도이다.

- 도 14b는 도 13에서 설명한 조립 기판을 라인 B-B'를 따라 자른 단면도이다.

- 도 15는 도 13 내지 14b에서 설명한 조립 기판의 회로도이다.

- 도 16은 도 15에서 설명한 회로에 인가되는 조립 신호를 나타내는 개념도이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0026] 이하, 첨부된 도면을 참조하여 본 명세서에 개시된 실시 예를 상세히 설명하되, 도면 부호에 관계없이 동일하거 나 유사한 구성요소는 동일한 참조 번호를 부여하고 이에 대한 중복되는 설명은 생략하기로 한다. 이하의 설명에서 사용되는 구성요소에 대한 접미사 "모듈" 및 "부"는 명세서 작성의 용이함만이 고려되어 부여되거나 혼용되는 것으로서, 그 자체로 서로 구별되는 의미 또는 역할을 갖는 것은 아니다. 또한, 본 명세서에 개시된 실시예를 설명함에 있어서 관련된 공지 기술에 대한 구체적인 설명이 본 명세서에 개시된 실시예의 요지를 흐릴 수 있다고 판단되는 경우 그 상세한 설명을 생략한다. 또한, 첨부된 도면은 본 명세서에 개시된 실시예를 쉽게 이해할 수 있도록 하기 위한 것일 뿐, 첨부된 도면에 의해 본 명세서에 개시된 기술적 사상이 제한되는 것으로 해석되어서는 아니 됨을 유의해야 한다.

- [0027] 또한, 층, 영역 또는 기판과 같은 요소가 다른 구성요소 "상(on)"에 존재하는 것으로 언급될 때, 이것은 직접적으로 다른 요소 상에 존재하거나 또는 그 사이에 중간 요소가 존재할 수도 있다는 것을 이해할 수 있을 것이다.

- [0028] 본 명세서에서 설명되는 디스플레이 장치에는 휴대폰, 스마트 폰(smart phone), 노트북 컴퓨터(laptop computer), 디지털방송용 단말기, PDA(personal digital assistants), PMP(portable multimedia player), 네비 게이션, 슬레이트 피씨(Slate PC), Tablet PC, Ultra Book, 디지털 TV, 디지털 사이니지, 헤드 마운팅 디스플레이(HMD), 데스크탑 컴퓨터 등이 포함될 수 있다. 그러나, 본 명세서에 기재된 실시 예에 따른 구성은 추후 개 발되는 새로운 제품형태이라도, 디스플레이가 가능한 장치에는 적용될 수도 있음을 본 기술분야의 당업자라면 쉽게 알 수 있을 것이다.

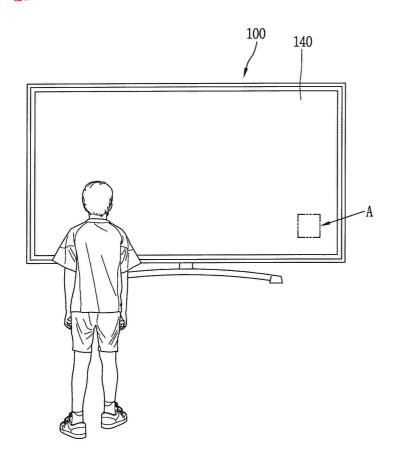

- [0029] 도 1은 본 발명의 반도체 발광 소자를 이용한 디스플레이 장치의 일 실시예를 나타내는 개념도이고, 도 2는 도 1의 디스플레이 장치의 A 부분의 부분 확대도이고, 도 3은 도 2의 반도체 발광소자의 확대도이며, 도 4는 도 2의 반도체 발광소자의 다른 실시예를 나타내는 확대도이다.

- [0030] 도시에 의하면, 디스플레이 장치(100)의 제어부에서 처리되는 정보는 디스플레이 모듈(140)에서 출력될 수 있다. 상기 디스플레이 모듈의 테두리를 감싸는 폐루프 형태의 케이스(101)가 상기 디스플레이 장치의 베젤을 형성할 수 있다.

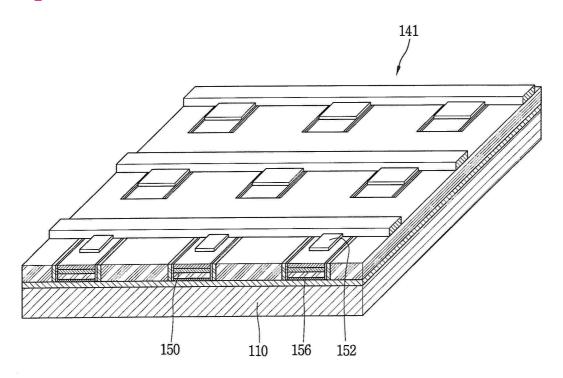

- [0031] 상기 디스플레이 모듈(140)은 영상이 표시되는 패널(141)을 구비하고, 상기 패널(141)은 마이크로 크기의 반도 체 발광소자(150)와 상기 반도체 발광소자(150)가 장착되는 배선기판(110)을 구비할 수 있다.

- [0032] 상기 배선기판(110)에는 배선이 형성되어, 상기 반도체 발광소자(150)의 n형 전극(152) 및 p형 전극(156)과 연결될 수 있다. 이를 통하여, 상기 반도체 발광소자(150)는 자발광하는 개별화소로서 상기 배선기판(110) 상에 구비될 수 있다.

- [0033] 상기 패널(141)에 표시되는 영상은 시각 정보로서, 매트릭스 형태로 배치되는 단위 화소(sub-pixel)의 발광이 상기 배선을 통하여 독자적으로 제어됨에 의하여 구현된다.

- [0034] 본 발명에서는 전류를 빛으로 변환시키는 반도체 발광소자(150)의 일 종류로서 마이크로 LED(Light Emitting Diode)를 예시한다. 상기 마이크로 LED는 100마이크로 이하의 작은 크기로 형성되는 발광 다이오드가 될 수 있다. 상기 반도체 발광소자(150)는 청색, 적색 및 녹색이 발광영역에 각각 구비되어 이들의 조합에 의하여 단위 화소가 구현될 수 있다. 즉, 상기 단위 화소는 하나의 색을 구현하기 위한 최소 단위를 의미하며, 상기 단위 화소 내에 적어도 3개의 마이크로 LED가 구비될 수 있다.

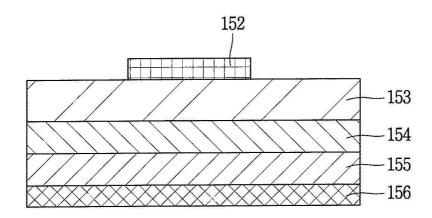

- [0035] 보다 구체적으로, 도 3을 참조하면, 상기 반도체 발광 소자(150)는 수직형 구조가 될 수 있다.

- [0036] 예를 들어, 상기 반도체 발광 소자(150)는 질화 갈륨(GaN)을 주로 하여, 인듐(In) 및/또는 알루미늄(Al)이 함께 첨가되어 청색을 비롯한 다양한 빛을 발광하는 고출력의 발광 소자로 구현될 수 있다.

- [0037] 이러한 수직형 반도체 발광 소자는 p형 전극(156), p형 전극(156) 상에 형성된 p형 반도체층(155), p형 반도체 층(155) 상에 형성된 활성층(154), 활성층(154)상에 형성된 n형 반도체층(153), 및 n형 반도체층(153) 상에 형성된 n형 전극(152)을 포함한다. 이 경우, 하부에 위치한 p형 전극(156)은 배선기판의 p전극과 전기적으로 연결될 수 있고, 상부에 위치한 n형 전극(152)은 반도체 발광소자의 상측에서 n전극과 전기적으로 연결될 수 있다. 이러한 수직형 반도체 발광 소자(150)는 전극을 상/하로 배치할 수 있으므로, 칩 사이즈를 줄일 수 있다는 큰 강점을 가지고 있다.

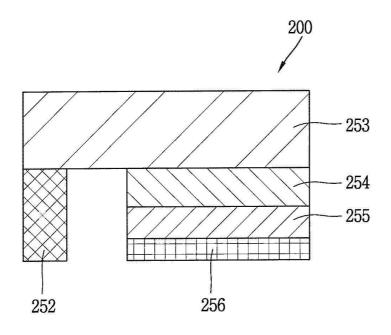

- [0038] 다른 예로서 도 4를 참조하면, 상기 반도체 발광 소자는 플립 칩 타입(flip chip type)의 발광 소자가 될 수 있

다.

- [0039] 이러한 예로서, 상기 반도체 발광 소자(250)는 p형 전극(256), p형 전극(256)이 형성되는 p형 반도체층(255), p 형 반도체층(255) 상에 형성된 활성층(254), 활성층(254) 상에 형성된 n형 반도체층(253), 및 n형 반도체층(253) 상에서 p형 전극(256)과 수평방향으로 이격 배치되는 n형 전극(252)을 포함한다. 이 경우, p형 전극(256)과 n형 전극(152)은 모두 반도체 발광소자의 하부에서 배선기판의 p전극 및 n전극과 전기적으로 연결될 수 있다.

- [0040] 상기 수직형 반도체 발광소자와 수평형 반도체 발광소자는 각각 녹색 반도체 발광소자, 청색 반도체 발광소자 또는 적색 반도체 발광소자가 될 수 있다. 녹색 반도체 발광소자와 청색 반도체 발광소자의 경우에 질화 갈륨 (GaN)을 주로 하여, 인듐(In) 및/또는 알루미늄(A1)이 함께 첨가되어 녹색이나 청색의 빛을 발광하는 고출력의 발광 소자로 구현될 수 있다. 이러한 예로서, 상기 반도체 발광소자는 n-Gan, p-Gan, AlGaN, InGan 등 다양한 계층으로 형성되는 질화갈륨 박막이 될 수 있으며, 구체적으로 상기 p형 반도체층은 P-type GaN 이고, 상기 n형 반도체층은 N-type GaN 이 될 수 있다. 다만, 적색 반도체 발광소자의 경우에는, 상기 p형 반도체층은 P-type GaAs 이고, 상기 n형 반도체층은 N-type GaAs 가 될 수 있다.

- [0041] 또한, 상기 p형 반도체층은 p 전극 쪽은 Mg가 도핑된 P-type GaN 이고, n형 반도체층은 n 전극 쪽은 Si가 도핑된 N-type GaN 인 경우가 될 수 있다. 이 경우에, 전술한 반도체 발광소자들은 활성층이 없는 반도체 발광소자가 될 수 있다.

- [0042] 한편, 도 1 내지 도 4를 참조하면, 상기 발광 다이오드가 매우 작기 때문에 상기 디스플레이 패널은 자발광하는 단위화소가 고정세로 배열될 수 있으며, 이를 통하여 고화질의 디스플레이 장치가 구현될 수 있다.

- [0043] 상기에서 설명된 본 발명의 반도체 발광 소자를 이용한 디스플레이 장치에서는 웨이퍼 상에서 성장되어, 메사 및 아이솔레이션을 통하여 형성된 반도체 발광소자가 개별 화소로 이용된다. 이 경우에, 마이크로 크기의 반도체 발광소자(150)는 웨이퍼에 상기 디스플레이 패널의 기판 상의 기설정된 위치로 전사되어야 한다. 이러한 전사기술로 픽앤플레이스(pick and place)가 있으나, 성공률이 낮고 매우 많은 시간이 요구된다. 다른 예로서, 스탬프나 롤을 이용하여 한 번에 여러개의 소자를 전사하는 기술이 있으나, 수율에 한계가 있어 대화면의 디스플레이에는 적합하지 않다. 본 발명에서는 이러한 문제를 해결할 수 있는 디스플레이 장치의 새로운 제조방법 및제조장치를 제시한다.

- [0044] 이를 위하여, 이하, 먼저 디스플레이 장치의 새로운 제조방법에 대하여 살펴본다. 도 5a 내지 도 5e는 전술한 반도체 발광 소자를 제작하는 새로운 공정을 설명하기 위한 개념도들이다.

- [0045] 본 명세서에서는, 패시브 매트릭스(Passive Matrix, PM) 방식의 반도체 발광 소자를 이용한 디스플레이 장치를 예시한다. 다만, 이하 설명되는 예시는 액티브 매트릭스(Active Matrix, AM) 방식의 반도체 발광 소자에도 적용 가능하다. 또한, 수평형 반도체 발광소자를 자가조립하는 방식에 대하여 예시하나, 이는 수직형 반도체 발광소자를 자가조립하는 방식에도 적용가능하다.

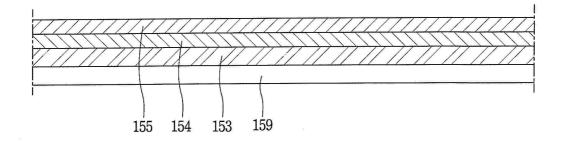

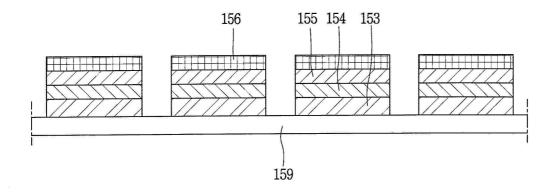

- [0046] 먼저, 제조방법에 의하면, 성장기판(159)에 제1도전형 반도체층(153), 활성층(154), 제2 도전형 반도체층(155)을 각각 성장시킨다(도 5a).

- [0047] 제1도전형 반도체층(153)이 성장하면, 다음은, 상기 제1도전형 반도체층(153) 상에 활성층(154)을 성장시키고, 다음으로 상기 활성층(154) 상에 제2도전형 반도체층(155)을 성장시킨다. 이와 같이, 제1도전형 반도체층(153), 활성층(154) 및 제2도전형 반도체층(155)을 순차적으로 성장시키면, 도 5a에 도시된 것과 같이, 제1도전형 반도체층(153), 활성층(154) 및 제2도전형 반도체층(155)이 적층 구조를 형성한다.

- [0048] 이 경우에, 상기 제1도전형 반도체층(153)은 p형 반도체층이 될 수 있으며, 상기 제2도전형 반도체층(155)은 n 형 반도체층이 될 수 있다. 다만, 본 발명은 반드시 이에 한정되는 것은 아니며, 제1도전형이 n형이 되고 제2도 전형이 p형이 되는 예시도 가능하다.

- [0049] 또한, 본 실시예에서는 상기 활성층이 존재하는 경우를 예시하나, 전술한 바와 같이 경우에 따라 상기 활성층이 없는 구조도 가능하다. 이러한 예로서, 상기 p형 반도체층은 Mg가 도핑된 P-type GaN 이고, n형 반도체층은 n 전극 쪽은 Si가 도핑된 N-type GaN 인 경우가 될 수 있다.

- [0050] 성장기판(159)(웨이퍼)은 광 투과적 성질을 가지는 재질, 예를 들어 사파이어(A1203), GaN, ZnO, A10 중 어느 하나를 포함하여 형성될 수 있으나, 이에 한정하지는 않는다. 또한, 성장기판(159)은 반도체 물질 성장에 적합한 물질, 캐리어 웨이퍼로 형성될 수 있다. 열 전도성이 뛰어난 물질로 형성될 수 있으며, 전도성 기판 또는 절

연성 기판을 포함하여 예를 들어, 사파이어(Al2O3) 기판에 비해 열전도성이 큰 SiC 기판 또는 Si, GaAs, GaP, InP, Ga2O3 중 적어도 하나를 사용할 수 있다.

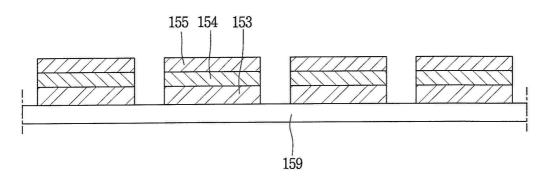

- [0051] 다음으로, 제1도전형 반도체층(153), 활성층(154) 및 제2 도전형 반도체층(155)의 적어도 일부를 제거하여 복수의 반도체 발광소자를 형성한다(도 5b).

- [0052] 보다 구체적으로, 복수의 발광소자들이 발광 소자 어레이를 형성하도록, 아이솔레이션(isolation)을 수행한다. 즉, 제1도전형 반도체층(153), 활성층(154) 및 제2 도전형 반도체층(155)을 수직방향으로 식각하여 복수의 반도체 발광소자를 형성한다.

- [0053] 만약, 수평형 반도체 발광소자를 형성하는 경우라면, 상기 활성층(154) 및 제2 도전형 반도체층(155)은 수직방 향으로 일부가 제거되어, 상기 제1도전형 반도체층(153)이 외부로 노출되는 메사 공정과, 이후에 제1도전형 반도체층을 식각하여 복수의 반도체 발광소자 어레이를 형성하는 아이솔레이션(isolation)이 수행될 수 있다.

- [0054] 다음으로, 상기 제2도전형 반도체층(155)의 일면 상에 제2도전형 전극(156, 또는 p형 전극)를 각각 형성한다(도 5c). 상기 제2도전형 전극(156)은 스퍼터링 등의 증착 방법으로 형성될 수 있으나, 본 발명은 반드시 이에 한정되는 것은 아니다. 다만, 상기 제1도전형 반도체층과 제2도전형 반도체층이 각각 n형 반도체층과 p형 반도체층인 경우에는, 상기 제2도전형 전극(156)은 n형 전극이 되는 것도 가능하다.

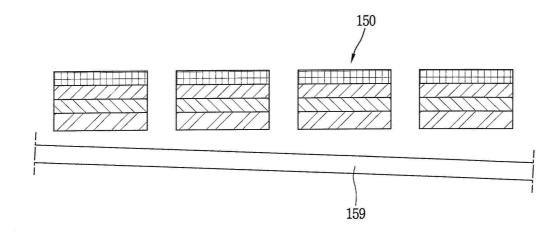

- [0055] 그 다음에, 상기 성장기판(159)을 제거하여 복수의 반도체 발광소자를 구비한다. 예를 들어, 성장기판(159)은 레이저 리프트 오프법(Laser Lift-off, LLO) 또는 화학적 리프트 오프법(Chemical Lift-off, CLO)을 이용하여 제거할 수 있다(도 5d).

- [0056] 이후에, 유체가 채워진 챔버에서 반도체 발광소자들(150)이 기판에 안착되는 단계가 진행된다(도 5e).

- [0057] 예를 들어, 유체가 채워진 챔버 속에 상기 반도체 발광소자들(150) 및 기판을 넣고 유동, 중력, 표면 장력 등을 이용하여 상기 반도체 발광소자들이 상기 기판(161)에 스스로 조립되도록 한다. 이 경우에, 상기 기판은 조립기판(161)이 될 수 있다.

- [0058] 다른 예로서, 상기 조립기판(161) 대신에 배선기판을 유체 챔버내에 넣어, 상기 반도체 발광소자들(150)이 배선 기판에 바로 안착되는 것도 가능하다. 이 경우에, 상기 기판은 배선기판이 될 수 있다. 다만, 설명의 편의상, 본 발명에서는 기판이 조립기판(161)으로서 구비되어 반도체 발광소자들(1050)이 안착되는 것을 예시한다.

- [0059] 반도체 발광소자들(150)이 조립기판(161)에 안착하는 것이 용이하도록, 상기 조립기판(161)에는 상기 반도체 발광소자들(150)이 끼워지는 셀들(미도시)이 구비될 수 있다. 구체적으로, 상기 조립기판(161)에는 상기 반도체 발광소자들(150)이 배선전극에 얼라인되는 위치에 상기 반도체 발광소자들(150)이 안착되는 셀들이 형성된다. 상기 반도체 발광소자들(150)은 상기 유체 내에서 이동하다가, 상기 셀들에 조립된다.

- [0060] 상기 조립기판(161)에 복수의 반도체 발광소자들이 어레이된 후에, 상기 조립기판(161)의 반도체 발광소자들을 배선기판으로 전사하면, 대면적의 전사가 가능하게 된다. 따라서, 상기 조립기판(161)은 임시기판으로 지칭될 수 있다.

- [0061] 한편, 상기에서 설명된 자가조립 방법은 대화면 디스플레이의 제조에 적용하려면, 전사수율을 높여야만 한다. 본 발명에서는 전사수율을 높이기 위하여, 중력이나 마찰력의 영향을 최소화하고, 비특이적 결합을 막는 방법과 장치를 제안한다.

- [0062] 이 경우, 본 발명에 따른 디스플레이 장치는, 반도체 발광소자에 자성체를 배치시켜 자기력을 이용하여 반도체 발광소자를 이동시키고, 이동과정에서 전기장을 이용하여 상기 반도체 발광소자를 기설정된 위치에 안착시킨다. 이하에서는, 이러한 전사 방법과 장치에 대하여 첨부된 도면과 함께 보다 구체적으로 살펴본다.

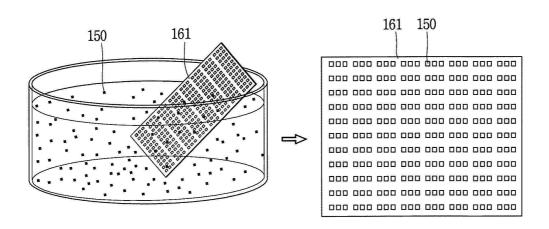

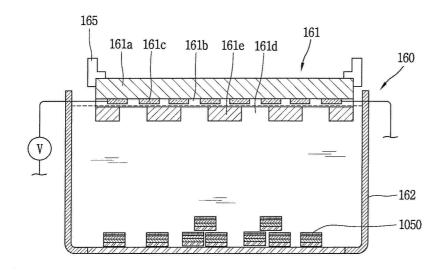

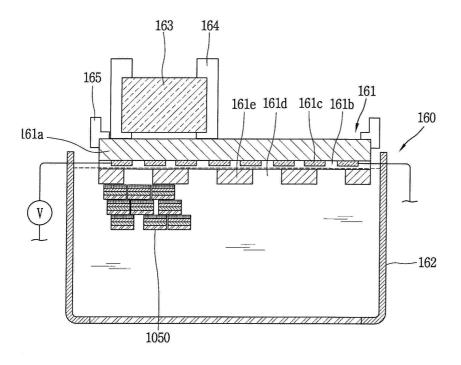

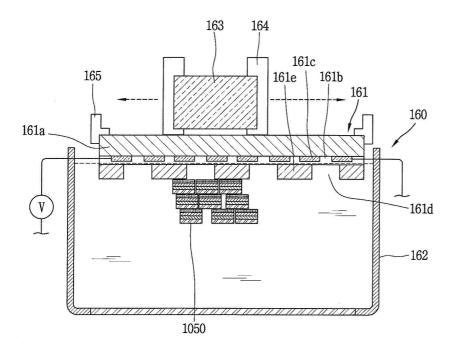

- [0063] 도 6은 본 발명에 따른 반도체 발광소자의 자가조립 장치의 일 예를 나타내는 개념도이고, 도 7은 도 6의 자가조립 장치의 블록 다이어그램이다. 또한, 도 8a 내지 도 8e는 도 6의 자가조립 장치를 이용하여 반도체 발광소자를 자가조립하는 공정을 나타내는 개념도이며, 도 9는 도 8a 내지 도 8e의 반도체 발광소자를 설명하기 위한 개념도이다.

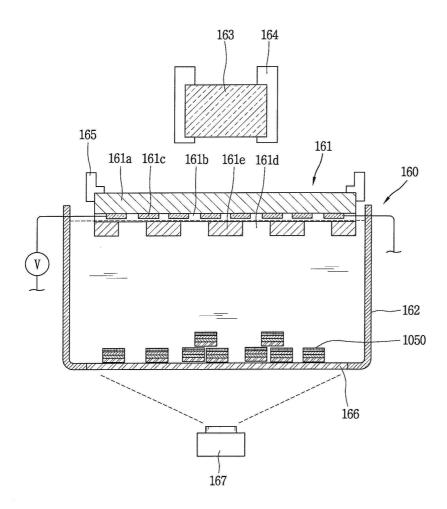

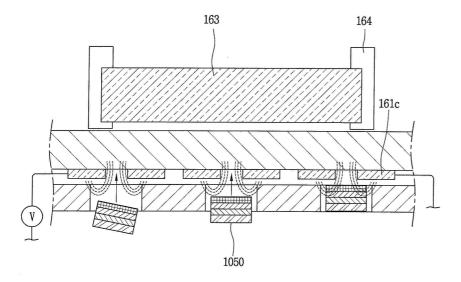

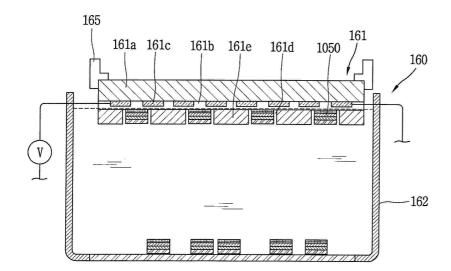

- [0064] 도 6 및 도 7의 도시에 의하면, 본 발명의 자가조립 장치(160)는 유체 챔버(162), 자석(163) 및 위치 제어부 (164)를 포함할 수 있다.

- [0065] 상기 유체 챔버(162)는 복수의 반도체 발광소자들을 수용하는 공간을 구비한다. 상기 공간에는 유체가 채워질

수 있으며, 상기 유체는 조립용액으로서 물 등을 포함할 수 있다. 따라서, 상기 유체 챔버(162)는 수조가 될 수 있으며, 오픈형으로 구성될 수 있다. 다만, 본 발명은 이에 한정되는 것은 아니며, 상기 유체 챔버(162)는 상기 공간이 닫힌 공간으로 이루어지는 클로즈형이 될 수 있다.

- [0066] 상기 유체 챔버(162)에는 기판(161)이 상기 반도체 발광소자들(150)이 조립되는 조립면이 아래를 향하도록 배치될 수 있다. 예를 들어, 상기 기판(161)은 이송부에 의하여 조립위치로 이송되며, 상기 이송부는 기판이 장착되는 스테이지(165)를 구비할 수 있다. 상기 스테이지(165)가 제어부에 의하여 위치조절되며, 이를 통하여 상기기판(161)은 상기 조립위치로 이송될 수 있다.

- [0067] 이 때에, 상기 조립위치에서 상기 기판(161)의 조립면이 상기 유체 챔버(150)의 바닥을 향하게 된다. 도시에 의하면, 상기 기판(161)의 조립면은 상기 유체 챔버(162)내의 유체에 잠기도록 배치된다. 따라서, 상기 반도체 발광소자(150)는 상기 유체내에서 상기 조립면으로 이동하게 된다.

- [0068] 상기 기판(161)은 전기장 형성이 가능한 조립기판으로서, 베이스부(161a), 유전체층(161b) 및 복수의 전극들 (161c)을 포함할 수 있다.

- [0069] 상기 베이스부(161a)는 절연성 있는 재질로 이루어지며, 상기 복수의 전극들(161c)은 상기 베이스부(161a)의 일 면에 패턴된 박막 또는 후막 bi-planar 전극이 될 수 있다. 상기 전극(161c)은 예를 들어, Ti/Cu/Ti 의 적층, Ag 페이스트 및 ITO 등으로 형성될 수 있다.

- [0070] 상기 유전체층(161b)은, SiO2, SiNx, SiON, Al2O3, TiO2, HfO2 등의 무기 물질로 이루어질 있다. 이와 다르게, 유전체층(161b)은, 유기 절연체로서 단일층이거나 멀티층으로 구성될 수 있다. 유전체층(161b)의 두께는, 수십 nm~수 u m의 두께로 이루어질 수 있다.

- [0071] 나아가, 본 발명에 따른 기판(161)은 격벽에 의하여 구획되는 복수의 셀들(161d)을 포함한다. 셀들(161d)은, 일 방향을 따라 순차적으로 배치되며, 폴리머(polymer) 재질로 이루어질 수 있다. 또한, 셀들(161d)을 이루는 격벽 (161e)은, 이웃하는 셀들(161d)과 공유되도록 이루어진다. 상기 격벽(161e)은 상기 베이스부(161a)에서 돌출되며, 상기 격벽(161e)에 의하여 상기 셀들(161d)이 일방향을 따라 순차적으로 배치될 수 있다. 보다 구체적으로, 상기 셀들(161d)은 열과 행 방향으로 각각 순차적으로 배치되며, 매트릭스 구조를 가질 수 있다.

- [0072] 셀들(161d)의 내부는, 도시와 같이, 반도체 발광소자(150)를 수용하는 홈을 구비하며, 상기 홈은 상기 격벽 (161e)에 의하여 한정되는 공간이 될 수 있다. 상기 홈의 형상은 반도체 발광소자의 형상과 동일 또는 유사할 수 있다. 예를 들어, 반도체 발광소자가 사각형상인 경우, 홈은 사각형상일 수 있다. 또한, 비록 도시되지는 않았지만, 반도체 발광소자가 원형인 경우, 셀들 내부에 형성된 홈은, 원형으로 이루어질 수 있다. 나아가, 셀들 각각은, 단일의 반도체 발광소자를 수용하도록 이루어진다. 즉, 하나의 셀에는, 하나의 반도체 발광소자가 수용된다.

- [0073] 한편, 복수의 전극들(161c)은 각각의 셀들(161d)의 바닥에 배치되는 복수의 전극라인을 구비하며, 상기 복수의 전극라인은 이웃한 셀로 연장되도록 이루어질 수 있다.

- [0074] 상기 복수의 전극들(161c)은 상기 셀들(161d)의 하측에 배치되며, 서로 다른 극성이 각각 인가되어 상기 셀들 (161d) 내에 전기장을 생성한다. 상기 전기장 형성을 위하여, 상기 복수의 전극들(161c)을 상기 유전체층이 덮으면서, 상기 유전체층이 상기 셀들(161d)의 바닥을 형성할 수 있다. 이런 구조에서, 각 셀들(161d)의 하측에서 한 쌍의 전극(161c)에 서로 다른 극성이 인가되면 전기장이 형성되고, 상기 전기장에 의하여 상기 셀들(161d) 내부로 상기 반도체 발광소자가 삽입될 수 있다.

- [0075] 상기 조립위치에서 상기 기판(161)의 전극들은 전원공급부(171)와 전기적으로 연결된다. 상기 전원공급부(171)는 상기 복수의 전극에 전원을 인가하여 상기 전기장을 생성하는 기능을 수행한다.

- [0076] 도시에 의하면, 상기 자가조립 장치는 상기 반도체 발광소자들에 자기력을 가하기 위한 자석(163)을 구비할 수 있다. 상기 자석(163)은 상기 유체 챔버(162)와 이격 배치되어 상기 반도체 발광소자들(150)에 자기력을 가하도록 이루어진다. 상기 자석(163)은 상기 기판(161)의 조립면의 반대면을 마주보도록 배치될 수 있으며, 상기 자석(163)과 연결되는 위치 제어부(164)에 의하여 상기 자석의 위치가 제어된다.

- [0077] 상기 자석(163)의 자기장에 의하여 상기 유체내에서 이동하도록, 상기 반도체 발광소자(1050)는 자성체를 구비할 수 있다.

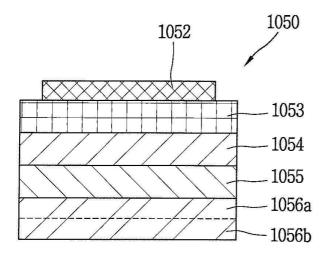

- [0078] 도 9를 참조하면, 자성체를 구비하는 반도체 발광 소자는 제1도전형 전극(1052) 및 제2도전형 전극(1056), 상기

제1도전형 전극(1052)이 배치되는 제1도전형 반도체층(1053), 상기 제1도전형 반도체층(1052)과 오버랩되며, 상기 제2도전형 전극(1056)이 배치되는 제2도전형 반도체층(1055), 그리고 상기 제1 및 제2도전형 반도체층(1053, 1055) 사이에 배치되는 활성층(1054)을 포함할 수 있다.

- [0079] 여기에서, 제1도전형은 p형이고, 제2도전형은 n형으로 구성될 수 있으며, 그 반대로도 구성될 수 있다. 또한, 전술한 바와 같이 상기 활성층이 없는 반도체 발광소자가 될 수 있다.

- [0080] 한편, 본 발명에서, 상기 제1도전형 전극(1052)는 반도체 발광소자의 자가조립 등에 의하여, 반도체 발광소자가 배선기판에 조립된 이후에 생성될 수 있다. 또한, 본 발명에서, 상기 제2도전형 전극(1056)은 상기 자성체를 포함할 수 있다. 자성체는 자성을 띄는 금속을 의미할 수 있다. 상기 자성체는 Ni, SmCo 등이 될 수 있으며, 다른 예로서 Gd 계, La계 및 Mn계 중 적어도 하나에 대응되는 물질을 포함할 수 있다.

- [0081] 자성체는 입자 형태로 상기 제2도전형 전극(1056)에 구비될 수 있다. 또한, 이와 다르게, 자성체를 포함한 도전 형 전극은, 도전형 전극의 일 레이어가 자성체로 이루어질 수 있다. 이러한 예로서, 도 9에 도시된 것과 같이, 반도체 발광소자(1050)의 제2도전형 전극(1056)은, 제1층(1056a) 및 제2층(1056b)을 포함할 수 있다. 여기에서, 제1층(1056a)은 자성체를 포함하도록 이루어질 수 있고, 제2층(1056b)는 자성체가 아닌 금속소재를 포함할 수 있다.

- [0082] 도시와 같이, 본 예시에서는 자성체를 포함하는 제1층(1056a)이, 제2도전형 반도체층(1055)과 맞닿도록 배치될수 있다. 이 경우, 제1층(1056a)은, 제2층(1056b)과 제2도전형 반도체층(1055) 사이에 배치된다. 상기 제2층 (1056b)은 배선기판의 제2전극과 연결되는 컨택 메탈이 될 수 있다. 다만, 본 발명은 반드시 이에 한정되는 것은 아니며, 상기 자성체는 상기 제1도전형 반도체층의 일면에 배치될 수 있다.

- [0083] 다시 도 6 및 도 7을 참조하면, 보다 구체적으로, 상기 자가조립 장치는 상기 유체 챔버의 상부에 x,y,z 축으로 자동 또는 수동으로 움직일 수 있는 자석 핸들러를 구비하거나, 상기 자석(163)을 회전시킬 수 있는 모터를 구비할 수 있다. 상기 자석 핸들러 및 모터는 상기 위치 제어부(164)를 구성할 수 있다. 이를 통하여, 상기 자석(163)은 상기 기판(161)과 수평한 방향, 시계방향 또는 반시계방향으로 회전하게 된다.

- [0084] 한편, 상기 유체 챔버(162)에는 광투과성의 바닥판(166)이 형성되고, 상기 반도체 발광소자들은 상기 바닥판 (166)과 상기 기판(161)의 사이에 배치될 수 있다. 상기 바닥판(166)을 통하여 상기 유체 챔버(162)의 내부를 모니터링하도록, 이미지 센서(167)가 상기 바닥판(166)을 바라보도록 배치될 수 있다. 상기 이미지 센서(167)는 제어부(172)에 의하여 제어되며, 기판(161)의 조립면을 관찰할 수 있도록 inverted type 렌즈 및 CCD 등을 구비할 수 있다.

- [0085] 상기에서 설명한 자가조립 장치는 자기장과 전기장을 조합하여 이용하도록 이루어지며, 이를 이용하면, 상기 반도체 발광소자들이 상기 자석의 위치변화에 의하여 이동하는 과정에서 전기장에 의하여 상기 기판의 기설정된 위치에 안착될 수 있다. 이하, 상기에서 설명한 자기조립 장치를 이용한 조립과정에 대하여 보다 상세히 설명한다

- [0086] 먼저, 도 5a 내지 도 5c에서 설명한 과정을 통하여 자성체를 구비하는 복수의 반도체 발광소자들(1050)을 형성한다. 이 경우에, 도 5c의 제2도전형 전극을 형성하는 과정에서, 자성체를 상기 반도체 발광소자에 증착할 수있다.

- [0087] 다음으로, 기판(161)을 조립위치로 이송하고, 상기 반도체 발광소자들(1050)을 유체 챔버(162)에 투입한다(도 8a).

- [0088] 전술한 바와 같이, 상기 기판(161)의 조립위치는 상기 기판(161)의 상기 반도체 발광소자들(1050)이 조립되는 조립면이 아래를 향하도록 상기 유체 챔버(162)에 배치되는 위치가 될 수 있다.

- [0089] 이 경우에, 상기 반도체 발광소자들(1050) 중 일부는 유체 챔버(162)의 바닥에 가라앉고 일부는 유체 내에 부유할 수 있다. 상기 유체 챔버(162)에 광투과성의 바닥판(166)이 구비되고, 상기 반도체 발광소자들(1050) 중 일부는 바닥판(166)에 가라앉을 수 있다.

- [0090] 다음으로, 상기 유체 챔버(162) 내에서 상기 반도체 발광소자들(1050)이 수직방향으로 떠오르도록 상기 반도체 발광소자들(1050)에 자기력을 가한다(도 8b).

- [0091] 상기 자가조립 장치의 자석(163)이 원위치에서 상기 기판(161)의 조립면의 반대면으로 이동하면, 상기 반도체 발광소자들(1050)은 상기 기판(161)을 향하여 상기 유체 내에서 떠오르게 된다. 상기 원위치는 상기 유체 챔버

(162)로부터 벗어난 위치가 될 수 있다. 다른 예로서, 상기 자석(163)이 전자석으로 구성될 수 있다. 이 경우에는 전자석에 전기를 공급하여 초기 자기력을 생성하게 된다.

- [0092] 한편, 본 예시에서, 상기 자기력의 크기를 조절하면 상기 기판(161)의 조립면과 상기 반도체 발광소자들(1050)의 이격거리가 제어될 수 있다. 예를 들어, 상기 반도체 발광소자들(1050)의 무게, 부력 및 자기력을 이용하여 상기 이격거리를 제어한다. 상기 이격거리는 상기 기판의 최외각으로부터 수 밀리미터 내지 수십 마이크로미터 가 될 수 있다.

- [0093] 다음으로, 상기 유체 챔버(162) 내에서 상기 반도체 발광소자들(1050)이 일방향을 따라 이동하도록, 상기 반도체 발광소자들(1050)에 자기력을 가한다. 예를 들어, 상기 자석(163)을 상기 기판과 수평한 방향, 시계방향 또는 반시계방향으로 이동한다(도 8c). 이 경우에, 상기 반도체 발광소자들(1050)은 상기 자기력에 의하여 상기 기판(161)과 이격된 위치에서 상기 기판(161)과 수평한 방향으로 따라 이동하게 된다.

- [0094] 다음으로, 상기 반도체 발광소자들(1050)이 이동하는 과정에서 상기 기판(161)의 기설정된 위치에 안착되도록, 전기장을 가하여 상기 반도체 발광소자들(1050)을 상기 기설정된 위치로 유도하는 단계가 진행된다(도 8c). 예를 들어, 상기 반도체 발광소자들(1050)이 상기 기판(161)과 수평한 방향으로 따라 이동하는 도중에 상기 전기 장에 의하여 상기 기판(161)과 수직한 방향으로 이동하여 상기 기판(161)의 기설정된 위치에 안착된다.

- [0095] 보다 구체적으로, 기판(161)의 bi-planar 전극에 전원을 공급하여 전기장을 생성하고, 이를 이용하여 기설정된 위치에서만 조립이 되도록 유도한게 된다. 즉 선택적으로 생성한 전기장을 이용하여, 반도체 발광소자들(1050)이 상기 기판(161)의 조립위치에 스스로 조립되도록 한다. 이를 위하여, 상기 기판(161)에는 상기 반도체 발광소자들(1050)이 끼워지는 셀들이 구비될 수 있다.

- [0096] 이후에, 상기 기판(161)의 언로딩 과정이 진행되며, 조립 공정이 완료된다. 상기 기판(161)이 조립 기판인 경우에, 전술한 바와 같이 어레인된 반도체 발광소자들을 배선기판으로 전사하여 디스플레이 장치를 구현하기 위한 후공정이 진행될 수 있다.

- [0097] 한편, 상기 반도체 발광소자들(1050)을 상기 기설정된 위치로 유도한 후에, 상기 유체 챔버(162) 내에 남아있는 반도체 발광소자들(1050)이 상기 유체 챔버(162)의 바닥으로 떨어지도록 상기 자석(163)을 상기 기판(161)과 멀어지는 방향으로 이동시킬 수 있다(도 8d). 다른 예로서, 상기 자석(163)이 전자석인 경우에 전원공급을 중단하면, 상기 유체 챔버(162) 내에 남아있는 반도체 발광소자들(1050)이 상기 유체 챔버(162)의 바닥으로 떨어지게된다.

- [0098] 이후에, 상기 유체 챔버(162)의 바닥에 있는 반도체 발광소자들(1050)을 회수하면, 상기 회수된 반도체 발광소자들(1050)의 재사용이 가능하게 된다.

- [0099] 상기에서 설명된 자가조립 장치 및 방법은 fluidic assembly에서 조립 수율을 높이기 위해 자기장을 이용하여 먼거리의 부품들을 미리 정해진 조립 사이트 근처에 집중시키고, 조립 사이트에 별도 전기장을 인가하여 조립 사이트에만 선택적으로 부품이 조립되도록 한다. 이때 조립기판을 수조 상부에 위치시키고 조립면이 아래로 향하도록 하여 부품의 무게에 의한 중력 영향을 최소화하면서 비특이적 결합을 막아 불량을 제거한다. 즉, 전사수율을 높이기 위해 조립 기판을 상부에 위치시켜 중력이나 마찰력 영향을 최소화하며, 비특이적 결합을 막는다.

- [0100] 이상에서 살펴본 것과 같이, 상기와 같은 구성의 본 발명에 의하면, 개별화소를 반도체 발광소자로 형성하는 디스플레이 장치에서, 다량의 반도체 발광소자를 한번에 조립할 수 있다.

- [0101] 한편, 상술한 자가 조립에 사용되는 전극들(161c, 이하 조립 전극이라 함) 사이에 형성되는 전기장에 세기는 상기 조립 전극들 각각에 인가되는 전압의 세기에 비례한다.

- [0102] 조립 전극들 사이에 형성되는 전기장의 세기가 너무 약할 경우, 반도체 발광소자가 기설정된 위치로 유도될 확률이 낮아질 뿐만 아니라, 기 조립된 반도체 발광소자가 기판으로부터 이탈할 가능성도 증가한다. 따라서, 조립 전극들 각각에 일정 크기 이상의 전압을 인가하는 것은 매우 중요하다.

- [0103] 하지만, 상술한 전원 공급부는 기설정된 전압보다 큰 전압을 인가할 수 없다. 따라서, 상술한 전원 공급부가 인가할 수 있는 전압 이상의 전압이 자가조립에 활용되어야 하는 경우, 별도의 증폭기가 필요해진다. 이로인하여, 자가 조립 장비의 복잡도가 상승하며, 공정 환경 및 재료 변동 시 유연성이 감소된다. 이에, 본 발명은별도의 추가 장비 없이 조립 전극에 인가되는 전압 신호를 증폭시킬 수 있는 구조를 제공한다.

- [0104] 이에 대한 설명에 앞서, 도 8a 내지 8e에서 설명한 조립 전극에 대하여 설명한다.

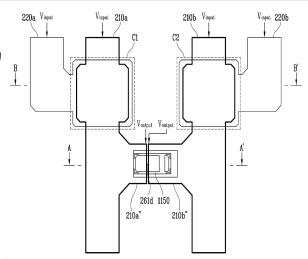

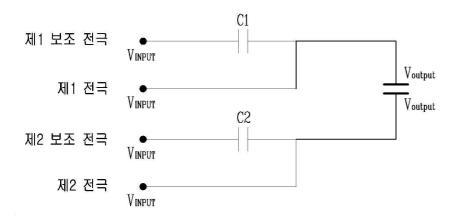

- [0105] 도 10은 도 8a 내지 8e에서 설명한 조립 전극을 나타낸 평면도이고, 도 11은 도 8a 내지 8e에서 설명한 조립 기판의 회로도이고, 도 12는 도 11에서 설명한 회로에 인가되는 조립 신호를 나타내는 개념도이다.

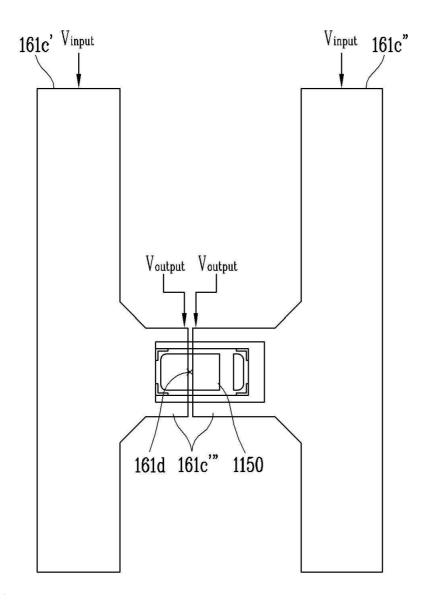

- [0106] 도 10을 참조하면, 조립 전극은 서로 인접하게 배치되는 제1전극(161c') 및 제2전극(161c'')을 포함할 수 있다. 상기 제1 및 제2전극161c' 및 161c'') 간의 거리는 상기 제1 및 제2전극(161c' 및 161c'')과 다른 조립 전극 간의 거리보다 작기 때문에, 조립 전극에 전압을 인가할 때 상기 제1 및 제2전극(161c' 및 161c'') 사이에 전기 장이 강하게 형성된다. 이 때문에, 자가조립 시 반도체 발광소자는 제1 및 제2전극(161c' 및 161c'') 사이로 유도된다.

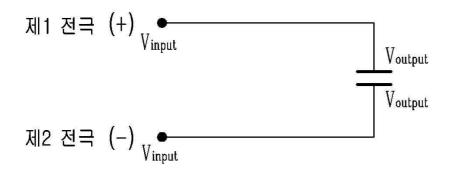

- [0107] 본 명세서에서 제1전극(161c')의 일단에는 전원 공급부가 연결되고 양(+)의 전압이 인가되며, 제2전극(161c'') 의 일단에는 전원 공급부가 연결되며 음(-)의 전압이 인가되는 것으로 설명한다. Vinput은 전원 공급부를 통해 조립 전극에 인가되는 전압의 크기를 의미한다. 한편, Voutput은 반도체 발광소자가 안착되어야 하는 위치(이하, 조립 위치)에서 측정되는 조립전극의 전압 신호를 의미한다. 자가조립 수율에 영향을 주는 전기장의 세기는 Voutput의 크기에 의해 결정된다.

- [0108] 본 명세서에서는 전원 공급부를 통해 인가되는 전압 신호를 Vinput이라하고, 조립 위치에서 측정되는 조립전국의 전압 신호를 Voutput이라 한다. 또한, 별도의 설명이 없는 경우, 제1전극(161c')에 인가되는 전압은 양(+)의 전압이며, 제2전극(161c'')에 인가되는 전압은 음(-)의 전압이다.

- [0109] 한편, 상기 제1 및 제2전극(161c' 및 161c'') 각각은 돌출부(161c''')를 구비할 수 있다. 상기 제1 및 제2전극 (161c' 및 161c'') 각각에 구비된 돌출부(161c''')는 서로 마주보도록 배치된다. 이에 따라, 상기 제1 및 제2전 극(161c' 및 161c'') 간의 거리가 가까워지면서 제1 및 제2전극(161c' 및 161c'') 사이에 형성되는 전기장의 세기가 증가될 수 있다. 상기 돌출부(161c''')는 조립 위치에 배치된다. 제1 및 제2전극(161c' 및 161c'') 각각이 돌출부(161c''')를 구비하는 경우, Voutput은 제1 및 제2전극(161c' 및 161c'') 각각에 구비된 돌출부 (161c''')의 일단에서 측정되는 전압 신호이다.

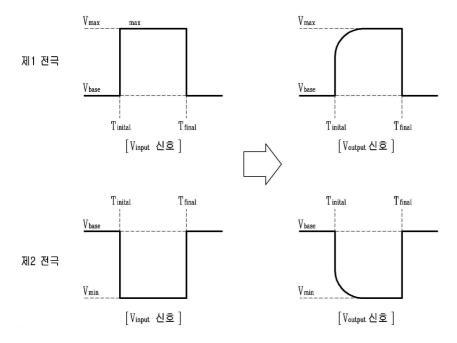

- [0110] 도 11을 참조하면, 제1 및 제2전극(161c' 및 161c'') 각각에 전압을 인가함에 따라, 조립 위치에는 Voutout의 전압 신호가 인가된다. 시간에 따른 Vinput 및 Voutput은 도 12에 도시되어 있다.

- [0111] 도 12를 참조하면, 전원 공급부는 제1전극(161c')에 Vmax 만큼의 전압을 인가한다. 이에 따라, 전압 인가를 시작한 시점(Tinitial)부터 전압 인가를 종료할 때(Tfinal)까지 제1전극(161c')의 Vinput은 Vmax가 된다. 여기서, Vmax는 전원 공급부에서 인가할 수 있는 전압의 최대값이다. 이에 따라, 제1전극(161c')의 Voutput은 Tinitial부터 서서히 증가하여 Vmax가 된다.

- [0112] 한편, 전원 공급부는 제2전극(161c'')에 Vmin 만큼의 전압을 인가한다. 이에 따라, 전압 인가를 시작한 시점 (Tinitial)부터 전압 인가를 종료할 때(Tfinal)까지 제2전극(161c'')의 Vinput은 Vmin가 된다. 여기서, Vmin는 전원 공급부에서 인가할 수 있는 전압의 최소값이다. 이에 따라, 제2전극(161c'')의 Voutput은 Tinitial부터 서서히 감소하여 Vmin이 된다.

- [0113] 이에 따라, 자가조립 중 제1전극(161c')에는 Vmax, 제2전극(161c'')에는 Vmin만큼의 전압이 인가된다. 상술한 바와 같이, 제1 및 제2전극(161c' 및 161c'') 사이의 전압차는 Vmax-Vmin 만큼 발생한다. 제1 및 제2전극(161c' 및 161c'') 사이에 형성되는 전기장의 세기를 증가시키고자 하는 경우, 제1 및 제2전극(161c' 및 161c'') 사이의 전압차를 증가시켜야 하나, 전원 공급부의 한계 전압으로 인하여, 제1 및 제2전극(161c' 및 161c'') 사이의 전압차는 Vmax-Vmin 보다 커질 수 없다. 본 발명은 별도의 전압 증폭기 없이 제1 및 제2전극(161c' 및 161c'') 사이의 전압차를 Vmax-Vmin보다 커질 수 있도록 하는 구조를 제공한다.

- [0114] 이하, 본 발명에 따른 조립 기판의 구조에 대하여 구체적으로 설명한다.

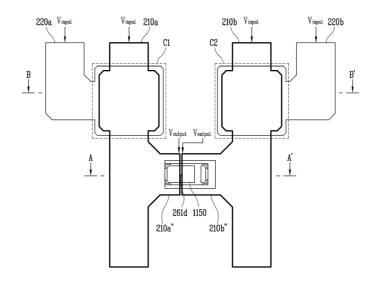

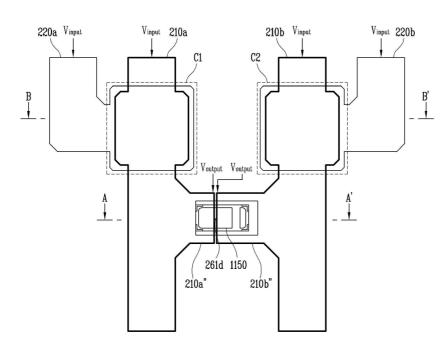

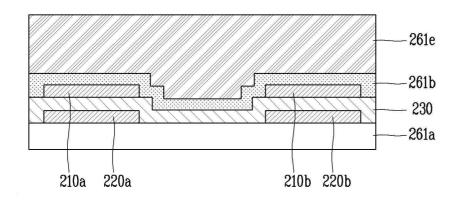

- [0115] 도 13은 본 발명에 따른 조립 기판을 나타내는 평면도이고, 도 14a는 도 13에서 설명한 조립 기판을 라인 A-A'를 따라 자른 단면도이고, 도 14b는 도 13에서 설명한 조립 기판을 라인 B-B'를 따라 자른 단면도이다.

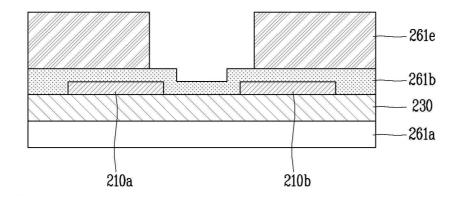

- [0116] 설명의 편의를 위하여 도 13에서 베이스부, 절연층, 격벽, 유전체층에 대한 도시는 생략하였으나, 도 14a 및 14b에 도시된 바와 같이, 본 발명에 따른 조립 기판은 베이스부, 절연층, 격벽, 유전체층을 구비할 수 있다.

- [0117] 도면을 참조하면, 본 발명에 따른 조립 기판은 베이스부, 복수의 보조 전극들, 절연층, 복수의 조립 전극들, 유전체층 및 격벽을 포함한다. 다만, 이에 한정되지 않고, 본 발명에 따른 조립 전극들은 상술한 구성요소보다 많거나 적은 구성을 포함할 수 있다.

- [0118] 이하, 상술한 구성요소에 대하여 구체적으로 설명한다.

- [0119] 상기 베이스부는 도 8a 내지 8e에서 설명한 베이스부와 동일하므로 구체적인 설명은 생략한다.

- [0120] 보조 전극은 상기 베이스부 상에 형성된다. 상기 베이스부 상에 배치되는 보조 전극의 개수는 후술할 조립 전극의 개수와 동일할 수 있다. 상기 보조 전극들 각각은 전원 공급부와 연결되며, 일부 영역이 조립 전극과 오버랩 되도록 배치된다. 상기 보조 전극은 후술할 조립 전극과 같이 일방향으로 따라 연장되도록 형성될 필요는 없다. 상기 보조 전극은 디스플레이 장치의 테두리에만 배치되어도 무방하다. 상기 보조 전극의 역할에 대하여는 후술한다.

- [0121] 상기 절연층은 상기 보조 전극을 덮도록 형성된다. 상기 절연층은 상기 보조 전극과 상기 조립 전극이 전기적으로 연결되지 않도록 하는 역할을 한다. 상기 절연층은 상기 베이스부 전 영역에 형성되거나, 상기 보조 전극과 상기 조립 전극이 오버랩되는 영역에만 부분적으로 형성될 수 있다. 첨부된 도면에서는 상기 절연층이 베이스부에 전 영역에 형성되는 실시 예를 도시하고 있으나, 이에 한정되지는 않는다.

- [0122] 한편, 조립 전극은 절연층 상에 배치된다. 상기 절연층에 의해 조립 전극과 보조 전극은 전기적으로 연결되지 않는다. 본 명세서에서는 도 10 내지 12에서 설명한 방식과 마찬가지로, 조립 전극을 제1 및 제2전극(210a 및 210b)으로 구분하여 설명한다.

- [0123] 조립 전극은 베이스부 상에 일방향을 따라 연장된다. 조립 전극의 일부 영역은 상기 보조 전극의 일부 영역과 오버랩되도록 배치된다. 일 실시 예에 있어서, 도 13을 참조하면, 제1전극(210a)은 제1보조 전극(220a)의 일부와 오버랩되도록 배치되고, 제2전극(210b)은 제2보조 전극(220b)의 일부와 오버랩되도록 배치된다.

- [0124] 상기 조립 전극과 상기 보조 전극이 오버랩되는 영역은 일정한 정전 용량을 가지는 캐패시터로 볼 수 있다. 예를 들어, 제1전극(210a)과 제1보조 전극(220a)이 오버랩되는 영역은 제1캐패시터(C1), 제2전극(210b)과 제2보조 전극(220b)이 오버랩되는 영역은 제2캐패시터(C2)로 볼 수 있다.

- [0125] 상술한 캐패시터의 정전용량이 클수록 Voutput이 커질 수 있다. 상술한 캐패시터의 정전용량을 증가시키기 위해, 본 발명에 따른 조립 전극들 각각은 조립 전극이 연장되는 방향과 교차하는 방향으로 돌출되는 제1돌출부를 구비한다. 상기 제1돌출부는 일방향으로만 돌출되도록 형성되거나, 서로 대향하는 방향으로 양방향으로 돌출 되도록 형성될 수 있다. 상기 보조 전극은 상기 제1돌출부와 오버랩되도록 배치된다.

- [0126] 일 실시 예에 있어서, 제1전극(210a)은 양방향으로 돌출되는 제1돌출부(210a')를 구비하고, 상기 제1보조 전극 (220a)는 상기 제1돌출부(210a')와 오버랩되도록 형성된다. 제2전극(210b)은 양방향으로 돌출되는 제1돌출부 (210b')를 구비하고, 상기 제2보조 전극(220b)는 상기 제1돌출부(210b')와 오버랩되도록 형성된다. 이를 통해, 본 발명은 상술한 캐패시터의 정전 용량을 증가시킨다.

- [0127] 상기 조립 전극과 상기 보조 전극이 오버랩되는 영역에서, 상기 조립 전극과 상기 보조 전극 사이의 정전용량은 1fF 내지 5000 μF인 것이 바람직하다. 이를 위해, 상기 조립 전극과 상기 보조 전극이 오버랩되는 면적은 100μm 2 내지 1m2일 수 있다.

- [0128] 한편, 상기 보조 전극들은 격벽에 형성되는 홈과 오버랩되지 않도록 형성될 수 있다. 이는 상기 보조 전극에 인 가되는 전압이 자가조립에 영향을 주는 것을 최소화 하기 위함이다.

- [0129] 일 실시 예에 있어서, 도 14a를 참조하면, 홈을 포함하는 조립 기판의 단면에는 보조 전극이 배치되지 않는다. 이와 달리, 도 14b를 참조하면, 홈이 형성되지 않는 다른 영역에는 조립 전극과 보조 전극이 오버랩되도록 배치 된다.

- [0130] 한편, 조립 전극 간의 거리를 좁히기 위해, 조립 전극들 각각은 상기 홈과 오버랩되도록 형성되며, 상기 조립 전극이 연장되는 방향과 교차하는 방향으로 돌출되는 제2돌출부를 구비한다. 본 발명은 홈 내부에 배치된 조립 전극들 간의 거리를 줄임으로써, 홈 내부에서의 전기장의 세기를 증가시킨다.

- [0131] 일 실시 예에 있어서, 제1 및 제2전극(210a 및 210b) 각각은 제2돌출부(210a'' 및 210b'')를 구비한다. 상기 두 개의 제2돌출부(210a'' 및 210b'')는 서로 마주보도록 배치된다. 후술할 Voutput은 상기 두 개의 돌출부(210a'' 및 210b'') 각각의 단부에서 측정되는 전압을 의미한다.

- [0132] 한편, 본 발명에 따른 조립 기판은 상기 조립 전극을 덮도록 형성되는 유전체층을 더 포함할 수 있다. 상기 유전체층(261b)는 도 8a 내지 8e에서 설명한 유전체층과 동일하므로 구체적이 설명은 생략한다.

- [0133] 이하, 상술한 조립 기판을 이용한 자가 조립 방법에 대하여 설명한다.

- [0134] 본 발명에 따른 자가 조립 방법은 조립 기판을 조립위치로 이송하고, 반도체 발광소자들을 유체 챔버에 투입하는 단계, 상기 유체 챔버 내에서 상기 반도체 발광소자들이 일방향을 따라 이동하도록, 상기 반도체 발광소자들에 자기력을 가하는 단계, 상기 반도체 발광소자들이 일 방향을 따라 이동하는 중 상기 조립 전극들 사이에 전 기장을 형성되는 전기장에 의하여 상기 반도체 발광소자들이 상기 홈 내부로 유도되도록, 상기 조립 전극들 사이에서 전기장을 발생시키는 단계를 포함한다. 상술한 단계들 중 상기 조립 전극들 사이에서 전기장을 발생시키는 단계를 제외한 단계들은 도 8a 내지 8e에서 설명한 내용과 동일하므로 구체적인 설명을 생략한다.

- [0135] 이하, 상기 조립 전극들 사이에서 전기장을 발생시키는 단계에 대하여 구체적으로 설명한다.

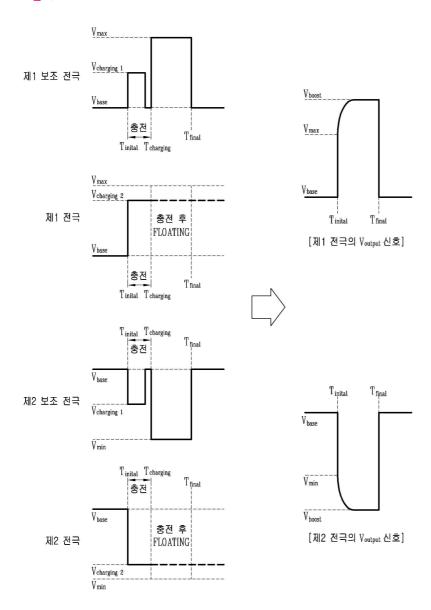

- [0136] 도 15는 도 13 내지 14b에서 설명한 조립 기판의 회로도이고, 도 16은 도 15에서 설명한 회로에 인가되는 조립 신호를 나타내는 개념도이다.

- [0137] 전원 공급부는 상기 조립 전극들 및 상기 보조 전극들 각각에 전압을 인가한다. 일 실시 예에 있어서, 전원 공급부는 제1 및 제2전극(210a 및 210b), 제1 및 제2보조 전극(220a 및 220b) 각각에 전압을 인가한다.

- [0138] 도 15를 참조하면, 제1 및 제2전극(210a 및 210b), 제1 및 제2보조 전극(220a 및 220b) 각각에 전압을 인가함에 따라 캐패시터 양단에는 전압이 인가된다. 여기서, 제1전극(210a)과 제1보조 전극(220a)이 서로 오버랩되는 영역을 제1캐패시터(C1)라 하고, 제2전극(210b)과 제2보조 전극(220b)이 서로 오버랩되는 영역을 제2캐패시터(C2)라 한다.

- [0139] 제1 및 제2전극(210a 및 210b), 제1 및 제2보조 전극(220a 및 220b) 각각에는 서로 다른 크기의 전압이 인가될 수 있으며, 각각의 전극에 인가되는 전압의 크기는 시간에 따라 달라질 수 있다.

- [0140] 상기 조립 전극들 사이에서 전기장을 발생시키는 단계는 크게 두 단계로 구분될 수 있다.

- [0141] 첫 번째, 상기 제1 및 제2캐패시터(C1 및 C2) 각각에 전하를 충전하는 단계가 수행된다. 구체적으로, 전원 공급 부는 조립 전극과 보조 전극 각각에 전압을 인가한다. 이때, 조립 전극에 인가되는 전압값의 절대값은 보조 전 극에 인가되는 전압값의 절대값보다 클 수 있다. 이에 따라, 조립 전극과 보조 전극이 오버랩되는 영역에 양 전 극의 전압차에 따른 전하가 충전된다.

- [0142] 일 실시 예에 있어서, 도 16을 참조하면, 전원공급부는 Tinitial 시점에 제1보조 전극(220a)에는 Vcharging1 만큼의 전압을 인가하고, 제1전극(210a)에는 Vcharging2 만큼의 전압을 인가한다. 여기서, Vcharging2의 절대값은 Vcharging1보다 클 수 있고, Vcharging1 및 Vcharging2는 Vmax보다 작다. 여기서, Vmax는 전원 공급부에서 인가할 수 있는 최대 전압을 의미한다.

- [0143] 전원 공급부는 Tinitial부터 Tcharging 까지 제1전극(210a)에 인가된 전압을 인가한다. 한편, 전원 공급부는 Tcharging이 되기 직전에 제1보조 전극(220a)에 인가되는 전압을 일시적으로 차단할 수 있다.

- [0144] Tinitial부터 Tcharging 까지 제1캐패시터에는 전하가 충전된다.

- [0145] 다른 일 실시 예에 있어서, 도 16을 참조하면, 전원공급부는 Tinitial 시점에 제2보조 전극(220b)에는 Vchargingl 만큼의 전압을 인가하고, 제2전극(210b)에는 Vcharging2 만큼의 전압을 인가한다. 여기서, Vcharging2의 절대값은 Vcharging1보다 클 수 있고, Vcharging1 및 Vcharging2는 Vmin보다 크다. 여기서, Vmin는 전원 공급부에서 인가할 수 있는 최소 전압을 의미한다.

- [0146] 전원 공급부는 Tinitial부터 Tcharging 까지 제2전극(210b)에 인가된 전압을 인가한다. 한편, 전원 공급부는 Tcharging이 되기 직전에 제2보조 전극(220b)에 인가되는 전압을 일시적으로 차단할 수 있다.

- [0147] 여기서, Vcharging1은 ±100V 일 수 있고, Vcharging2는 ±200V 일 수 있다.

- [0148] 상술한 바와 같이, 본 발명은 조립 전극과 보조 전극 각각에 서로 다른 전압을 인가함으로써, 조립 전극과 보조 전극이 오버랩되는 영역에 전하가 충전되도록 한다.

- [0149] 이후, 상기 조립 전극들과 상기 보조 전극들 사이에 충전된 전하를 이용하여 상기 조립 전극들 각각에 인가되는 전압의 크기를 증폭시키는 단계가 진행된다.

- [0150] 전원 공급부는 상기 조립 전극들과 상기 보조 전극들 사이에 전하가 충분히 충전된 후, 상기 조립 전극들에 인 가되는 전압을 차단하고, 상기 보조 전극들에 인가되는 전압의 절대값을 증가시킨다. 이때, 상기 조립 전극들과

상기 보조 전극들 사이에 충전된 전하로 인하여 Voutput 값이 증가하게 된다.

- [0151] 일 실시 예에 있어서, 전원 공급부는 Tcharging 시점 이후 제1보조 전극(220a)에 인가되는 전압을 Vmax까지 증가시키고, 제1전극(210a)에 인가되는 전압을 차단한다. 이에 따라, Voutput 신호값이 Vboost 값까지 증가한다. 여기서, Vboost 값은 Vmax보다 크다. 즉, Voutput 신호값이 전원 공급부가 인가할 수 있는 최대 전압값보다 커진다.

- [0152] 다른 일 실시 예에 있어서, 전원 공급부는 Tcharging 시점 이후 제2보조 전극(220b)에 인가되는 전압을 Vmin까지 감소시키고, 제2전극(210b)에 인가되는 전압을 차단한다. 이에 따라, Voutput 신호값이 Vboost 값까지 감소한다. 여기서, Vboost 값은 Vmin보다 작다. 즉, Voutput 신호값이 전원 공급부가 인가할 수 있는 최소 전압값보다 작아진다.

- [0153] 상술한 바와 같이, 충전 및 증폭 단계를 수행함에 따라, 제1 및 제2전극(210a 및 210b) 사이에는 Vmax-Vmin 값 보다 큰 전압 차이가 형성된다.

- [0154] 여기서, Vmax는 300V이고, Vmin은 -300V일 수 있다.

- [0155] 상술한 바와 같이, 본 발명은 보조 전극과 조립 전극이 오버랩되는 영역에 전하를 충전시킨 후 이를 활용하여 조립 전극에 인가되는 전압 신호의 크기를 증가시킨다. 이를 통해, 본 발명은 별도의 증폭 장치 없이 조립 전극들 사이에 형성되는 전기장의 세기를 증가시킬 수 있게 된다.

#### 도면

도면2

도면4

# 도면5a

# 도면5b

## 도면5c

## 도면5d

## 도면5e

## 도면8a

# 도면8b

# 도면8c

# 도면8d

# *도면8e*

# 도면12

# 도면14a

## 도면14b

| 专利名称(译)     | 显示装置的制造方法和显示装置的基板                                         |         |            |

|-------------|-----------------------------------------------------------|---------|------------|

| 公开(公告)号     | KR1020200024177A                                          | 公开(公告)日 | 2020-03-06 |

| 申请号         | KR1020200019246                                           | 申请日     | 2020-02-17 |

| 申请(专利权)人(译) | LG电子公司                                                    |         |            |

| [标]发明人      | 장재원<br>김수현                                                |         |            |

| 发明人         | 장재원<br>김수현                                                |         |            |

| IPC分类号      | H01L27/15 G09F9/33 H01L21/768 H01L33/00                   |         |            |

| CPC分类号      | H01L27/156 G09F9/33 H01L21/76895 H01L33/005 H01L2224/0344 |         |            |

| 代理人(译)      | 박장원                                                       |         |            |

| 外部链接        | Espacenet                                                 |         |            |

#### 摘要(译)

显示装置的制造方法技术领域本发明涉及显示装置的制造方法。 具体地,本发明涉及使用尺寸为几µm至几十µm的半导体发光元件制造显示装置的方法,以及用于制造显示装置的组装基板。 为此,提供了一种在显示装置的制造方法中使用的组装基板,该显示基板利用电场和磁场来将半导体发光元件安装在组装基板的预定位置。 更具体地,组装基板包括:基部;和 在基部上形成辅助电极; 绝缘层形成在基部上以覆盖辅助电极; 多个组装电极设置在绝缘层上; 隔壁形成在基部上,并且具有将半导体发光元件引导到预定位置的多个凹槽。 一些辅助电极被布置为与组装电极重叠。 根据本发明,在其中各个像素由微发光二极管形成的显示装置中,可以一次组装大量的半导体发光元件。